# M54HC221/221A M74HC221/221A

# **DUAL MONOSTABLE MULTIVIBRATOR**

- HIGH SPEED tpp = 25 ns (TYP) at Vcc = 5V

- LOWPOWER DISSIPATION STANDBYSTATE Icc=4 µA (MAX.) AT TA=25°C ACTIVE STATE Icc = 700 µA (MAX.) AT Vcc=5V

- HIGH NOISE IMMUNITY

VNIH = VNIL = 28 % VCC (MIN.)

- OUTPUT DRIVE CAPABILITY

10 LSTTL LOADS

- SYMMETRICAL OUTPUT IMPEDANCE IOH = IOL = 4 mA (MIN.)

- BALANCED PROPAGATION DELAYS tplh = tphL

- WIDE OPERATING VOLTAGE RANGE Vcc (OPR) = 2 V TO 6 V

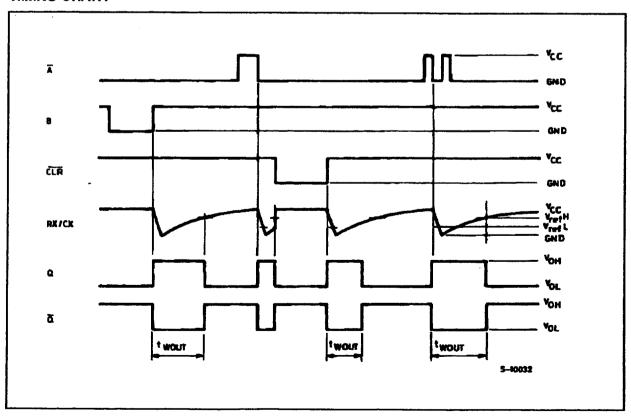

- WIDE OUTPUT PULSE WIDTH RANGE twout = 150 ns ~ 60 s OVER AT Vcc = 4.5 V

- PIN AND FUNCTION COMPATIBLE WITH 54/74LS221

#### DESCRIPTION

The M54/74HC221/221A are high speed CMOS MONOSTABLE multivibrators fabricated with silicon gate C<sup>2</sup>MOS technology. It achieves the high speed operation similar to equivalent LSTTL while maintaining the CMOS low power dissipation. There are two trigger inputs, AINPUT (negative edge) and B INPUT (positive edge). Triggering on the B input occurs at a particular voltage threshold and is not related to the rise and fall time of the applied pulse. The device may also be triggered by using the CLR input (positive-edge) because of the Schmitt-trigger input; after triggering the output maintains the MONOSTABLE state for the time period determined by the external resistor Rx and capacitor Cx. Taking CLR low breaks this MONOSTABLE STATE. If the next trigger pulse occurs during the MONOSTABLE period it makes the MONOSTABLE period longer. Limit for values of Cx and Rx:

Cx: NO LIMIT

Rx:  $V_{CC} < 3.0 \text{ V } 5 \text{ K } \Omega \text{ to 1 M } \Omega$  $V_{CC} \ge 3.0 \text{ V 1 K } \Omega \text{ to 1 M } \Omega$

Two different pulse width constants are available:  $K \cong 0.7$  for HC221

K≅1 for HC221A

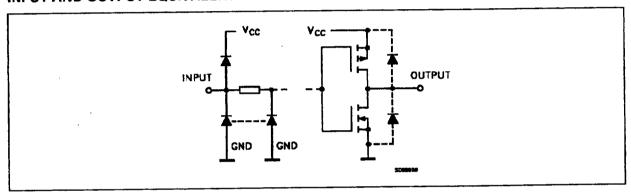

All inputs are equipped with protection circuits against static discharge and transient excess voltage.

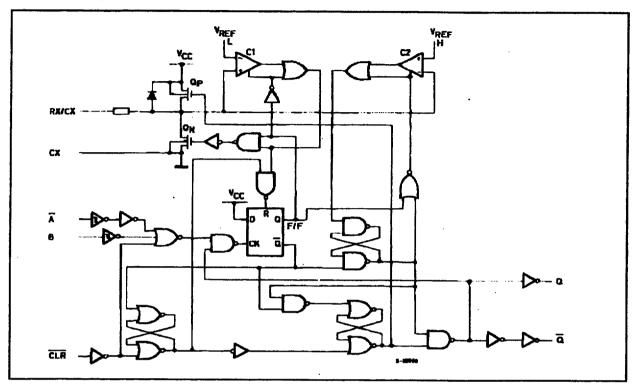

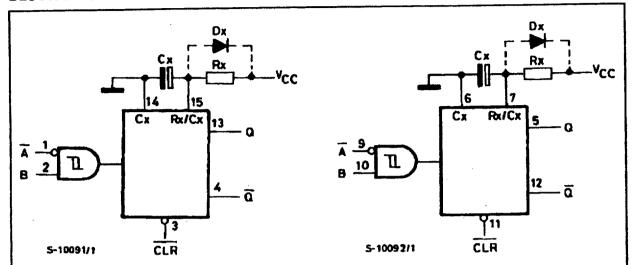

# SYSTEM DIAGRAM

# TIMING CHART

|              | BEP Métiers de l'électronique | 1    | S    | Doc const |

|--------------|-------------------------------|------|------|-----------|

| Code examen: | BEP Metters de l'electronique | l    | 0001 | 2/8       |

| 51025504     |                               | EP1A | 2001 | 2/0       |

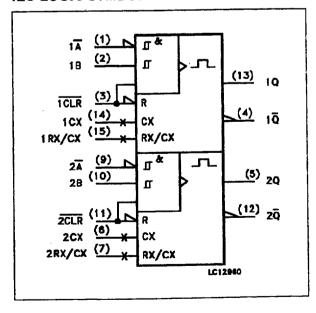

#### BLOCK DIAGRAM

#### Note:

- (1) Cx, Rx, Dx are external components.

- (2) Dx is a clamping diode.

The external capacitor is charged to Vcc in the stand-by state, i.e. no trigger. When the supply voltage is turned off Cx is discharged mainly through an internal parasitic diode (see figures). If Cx is sufficiently large and Vcc decreases rapidy, there will be some possibility of damaging the I.C. with a surge current or latch-up. If the voltage supply filter capacitor is large enough and Vcc decrease slowly, the surge current is automatically limited and damage the I.C. is avoided. The maximum forward current of the parasitic diode is approximately 20 mA. In cases where Cx is large the time taken for the supply voltage to fall to 0.4 Vcc can be calculated as follows:

t<sub>i</sub> ≥ (Vcc - 0.7) · Cx/20mA

In cases where it is too short an external clamping diode is required to protect the I.C. from the surge current.

#### **FUNCTIONAL DESCRIPTION**

#### STAND-BY STATE

The external capacitor, Cx, is fully charged to Vcc in the stand-by state. Hence, before triggering, transistor Qp and Qn (connected to the Rx/Cx node) are both turned-off. The two comparators that control the timing and the two reference voltage sources stop operating. The total supply current is therefore only leakage current.

## TRIGGER OPERATION

Triggering occurs when:

1<sup>st</sup>) A is "low" and B has a falling edge; 2<sup>nd</sup>) B is "high" and A has a rising edge;

3<sup>rd</sup>) A is low and B is high and C1 has a rising edge.

After the multivibrator has been retriggered comparator C1 and C2 start operating and Qn is turned on. Cx then discharges through Qn. The voltage at the node R/C external falls.

When it reaches VREFL the output of comparator C1 becomes low. This in turn resets the flip-flop and Qn is turned off.

At this point C1 stops functioning but C2 continues to operate

The voltage at R/C external begins to rise with a time constant set by the external components Rx, Cx.

Triggering the multivibrator causes Q to go high after internal delay due to the flip-flop and the gate. Q remains high until the voltage at R/C external rises again to VREFH. At this point C2 output goes low and O goes low. C2 stop operating. That means that after triggering when the voltage R/C external returns to VREFH the multivibrator has returned to its MONOSTABLE STATE. In the case where Rx · Cx are large enough and the discharge time of the capacitor and the delay time in the I.C. can be ignored, the width of the output pulse tw (out) is as follows:

> $t_{W(OUT)} = 0.70 Cx \cdot Rx (HC221)$  $t_{W(OUT)} = Cx \cdot Rx (HC221A)$

## RESET OPERATION

CL is normally high. If CL is low, the trigger is not effective because Q output goes low and trigger control flip-flop is reset.

Also transistor Op is turned on and Cx is charged quicky to Vcc. This means if CL input goes low, the IC becomes waiting state both in operating and non operation state.

#### TRUTH TABLE

|          | INPUTS |     |       | PUTS  | NOTE          |

|----------|--------|-----|-------|-------|---------------|

| Ā        | В      | CLR | D     | Q     |               |

| 7        | Н      | Н   |       |       | OUTPUT ENABLE |

| X        | L      | Н   | L (*) | H (*) | INHIBIT       |

| H        | X      | Н   | L (*) | H (*) | INHIBIT       |

| 1        | Г      | Н   |       |       | OUTPUT ENABLE |

|          | Н      |     |       |       | OUTPUT ENABLE |

| <u> </u> | X      | L   | L     | Н     | INHIBIT       |

X: Don't Care (\*): Except for monostble period

# INPUT AND OUTPUT EQUIVALENT CIRCUIT

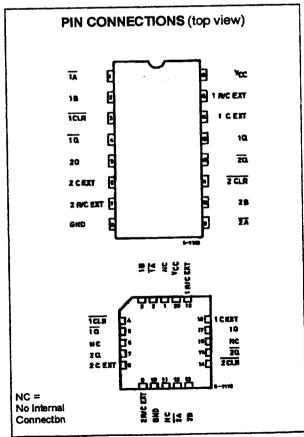

# PIN DESCRIPTION

| PIN No | SYMBOL                              | NAME AND FUNCTION                                          |

|--------|-------------------------------------|------------------------------------------------------------|

| 1, 9   | 1Ā, 2Ā                              | Trigger Inputs (Negative Edge Triggered)                   |

| 2, 10  | 1B, 2B                              | Trigger Inputs (Positive Edge Triggered)                   |

| 3, 11  | 1CLR,<br>2CLR                       | Direct Reset LOW and<br>Trigger Action at Positive<br>Edge |

| 4, 12  | 1Q, 2Q                              | Outputs (Active LOW)                                       |

| 7      | 2REXT/CEXT                          | External Resistor Capacitor Connection                     |

| 13, 5  | 1Q, 2Q                              | Outputs (Active HIGH)                                      |

| 14, 6  | 1C <sub>EXT</sub>                   | External Capacitor Connection                              |

| 15     | 1R <sub>EXT</sub> /C <sub>EXT</sub> | External Resistor Capacitor Connection                     |

| 8      | GND                                 | Ground (0V)                                                |

| 16     | Vcc                                 | Positive Supply Voltage                                    |

# **IEC LOGIC SYMBOL**

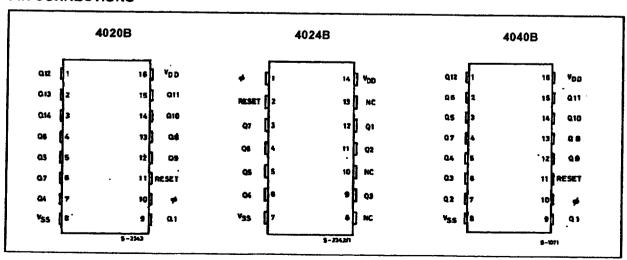

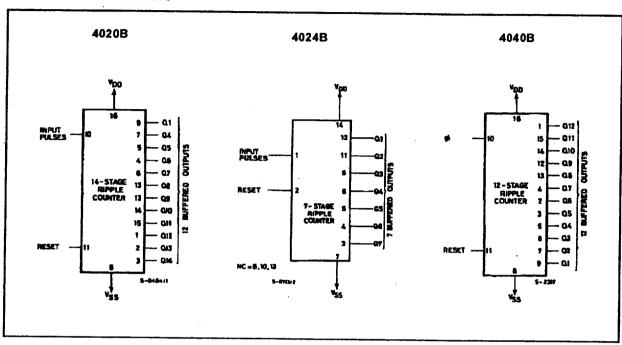

# HCC4020B/24B/40B HCF4020B/24B/40B

# RIPPLE-CARRY BINARY COUNTER/DIVIDERS

4020B - 14 STAGE

4024B - 7 STAGE

4040B - 12 STAGE

- MEDIUM-SPEED OPERATION

- FULLY STATIC OPERATION

- **COMMON RESET**

- BUFFERED INPUTS AND OUTPUTS

- QUIESCENT CURRENT SPECIFIED TO 20V FOR HCC DEVICE

- STANDARDIZED SYMMETRICAL OUTPUT

- CHARACTERISTICS

- 5V, 10V, AND 15V PARAMETRIC RATINGS

- INPUT CURRENT OF 100nA AT 18V AND 25°C FOR HCC DEVICE

- 100% TESTED FOR QUIESCENT CURRENT

- MEETS ALL REQUIREMENTS OF JEDEC TEN-TATIVE STANDARD No. 13A, "STANDARD SPECIFICATIONS FOR DESCRIPTION OF "B" SERIES CMOS DEVICES"

#### **DESCRIPTION**

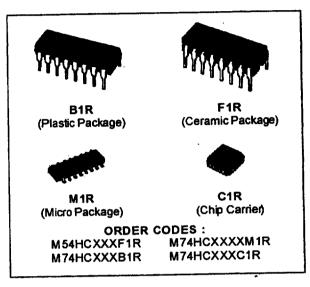

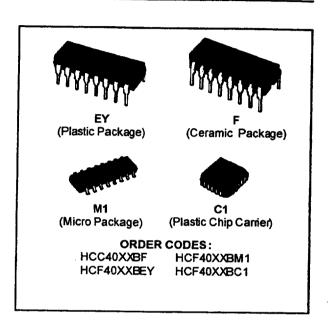

The HCC4XXXB (extended temperature range) and HCF4XXXB (intermediate temperature range) are monolithic integrated circuits, available in 14-lead dual in-line for 4024B and 16-lead dual in-line for 4020B, 4040B plastic or ceramic package and plastic micropackage.

The HCC/HCF4020B, 4024B, and 4040B are ripplecarry binary counters. All counter stages are masterslave flip-flops. The state of a counter advances one count on the negative transition of each input pulse; a high level on the RESET line resets the counter to its all zeros stage. Schmitt trigger action on the inputpulse line permits unlimited clock rise and fall times. All inputs and outputs are buffered.

#### **PIN CONNECTIONS**

|   | Code examen: | BEP Métiers de l'électronique | FD4 A | S 2001 | Doc const<br>5/8 |

|---|--------------|-------------------------------|-------|--------|------------------|

| j | 51025504     |                               | EP1A  | 2001   | 9/8              |

# **FUNCTIONAL DIAGRAMS**

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                                                               | Value                          | Unit |

|-------------------|-------------------------------------------------------------------------|--------------------------------|------|

| V <sub>DD</sub> * | Supply Voltage : HCC Types HCF Types                                    | - 0.5 to + 20<br>- 0.5 to + 18 | V    |

| Vı                | Input Voltage                                                           | - 0.5 to V <sub>DD</sub> + 0.5 | V    |

| l <sub>l</sub>    | DC Input Current (any one input)                                        | ± 10                           | mA   |

| P <sub>tot</sub>  | Total Power Dissipation (per package) Dissipation per Output Transistor | 200                            | mW   |

|                   | for Top = Full Package-temperature Range                                | 100                            | mW   |

| Тор               | Operating Temperature : HCC Types HCF Types                             | - 55 to + 125<br>- 40 to + 85  | င့   |

| T <sub>stg</sub>  | Storage Temperature                                                     | - 65 to + 150                  | -€   |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for external periods may affect device reliability.

\* All voltage values are refered to Vss pin voltage.

# RECOMMENDED OPERATING CONDITIONS

| Symbol          | Parameter                                   | Value                         | Unit |

|-----------------|---------------------------------------------|-------------------------------|------|

| V <sub>DD</sub> | Supply Voltage : HCC Types HCF Types        | 3 to 18<br>3 to 15            | V    |

| Vı              | Input Voltage                               | 0 to V <sub>DD</sub>          | V    |

| Тор             | Operating Temperature : HCC Types HCF Types | - 55 to + 125<br>- 40 to + 85 | ဗင   |

| Code examen: | BEP Métiers de l'électronique |      | S    | Doc const |

|--------------|-------------------------------|------|------|-----------|

| 51025504     |                               | EP1A | 2001 | 6/8       |

National Semiconductor

March 1988

3.0V to 15V

0.45 V<sub>DD</sub> (typ.)

or 1 driving 74LS

5.0 MHz (typ.)

with 10V V<sub>DD</sub>

10 μW (typ.)

Fan out of 2 driving 74L

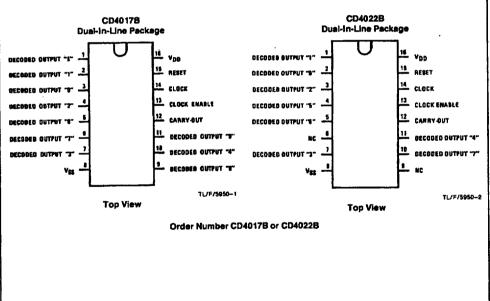

# CD4017BM/CD4017BC Decade Counter/Divider with 10 Decoded Outputs CD4022BM/CD4022BC Divide-by-8 Counter/Divider with 8 Decoded Outputs

# **General Description**

The CD4017BM/CD4017BC is a 5-stage divide-by-10 Johnson counter with 10 decoded outputs and a carry out bit.

The CD4022BM/CD4022BC is a 4-stage divide-by-8 Johnson counter with 8 decoded outputs and a carry-out bit.

These counters are cleared to their zero count by a logical "1" on their reset line. These counters are advanced on the positive edge of the clock signal when the clock enable signal is in the logical "0" state.

The configuration of the CD4017BM/CD4017BC and CD4022BM/CD4022BC permits medium speed operation and assures a hazard free counting sequence. The 10/8 decoded outputs are normally in the logical "0" state and go to the logical "1" state only at their respective time slot. Each decoded output remains high for 1 full clock cycle. The carry-out signal completes a full cycle for every 10/8 clock input cycles and is used as a ripple carry signal to any succeeding stages.

#### **Features**

- Wide supply voltage range

- High noise immunity

- In Low power TTL compatibility

- m Medium speed operation

- m Low power

- Fully static operation

### **Applications**

- Automotive

- Instrumentation

- Medical electronics

- Alarm systems ■ Industrial electronics

- Remote metering

# **Connection Diagrams**

F1395 National Semiconductor Corporation 11./F/595

PPID-830M105/Printed in U. S. A

Code examen: BEP Métiers de l'électronique 51025504

S 2001

EP1A

Dec Const 7/8

| Symbol                 | Parameter                                | and t <sub>ICL</sub> = 20 ns, unless otherwise sp<br>Conditions                               | Min | Тур               | Max                | Units          |

|------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------|-----|-------------------|--------------------|----------------|

| SET OPERA              | TION                                     |                                                                                               |     |                   |                    |                |

| <sup>t</sup> PHL, tPLH | Propagation Dalay Time<br>Carry Out Line | V <sub>DO</sub> = 5V<br>V <sub>DO</sub> = 10V<br>V <sub>DO</sub> = 15V                        |     | 415<br>160<br>130 | 800<br>320<br>250  | ns<br>ns<br>ns |

|                        | Carry Out Line                           | $ \begin{vmatrix} V_{DD} = 5V \\ V_{DD} = 10V \\ V_{DD} = 15V \end{vmatrix} $ $C_{L} = 15 pF$ |     | 240<br>85<br>70   | 480<br>170<br>140  | ns<br>ns<br>ns |

|                        | Decode Out Lines                         | V <sub>DD</sub> = 5V<br>V <sub>DD</sub> = 10V<br>V <sub>DD</sub> = 15V                        |     | 500<br>200<br>160 | 1000<br>400<br>320 | ns<br>ns<br>ns |

| w                      | Minimum Reset<br>Pulse Width             | V <sub>DD</sub> = 5V<br>V <sub>DD</sub> = 10V<br>V <sub>DD</sub> = 15V                        |     | 200<br>70<br>55   | 400<br>140<br>110  | ns<br>ns<br>ns |

| <sup>L</sup> REM       | Minimum Reset<br>Removal Time            | V <sub>DD</sub> = 5V<br>V <sub>DD</sub> = 10V<br>V <sub>DD</sub> = 15V                        |     | 75<br>30<br>25    | 150<br>60<br>50    | ns<br>ns<br>ns |

| *AC Parameters         | are guaranteed by DC correlated tes      | ling.                                                                                         |     |                   |                    |                |

| ,                      | CLOCK (NABLE )                           | 2                                                                                             |     |                   |                    |                |

|                        | -3.                                      | J 3\                                                                                          |     |                   |                    |                |

|                        | -4                                       |                                                                                               |     |                   |                    |                |

|                        | "4"<br>"5"                               |                                                                                               |     |                   |                    |                |

|                        | ~4··                                     |                                                                                               |     |                   |                    |                |

|                        | ~4··                                     |                                                                                               |     |                   |                    |                |

| Code examen'. | BEP Métiers de l'électronique | FR4 A | S<br>2001 | Boc Const<br>8/8 |

|---------------|-------------------------------|-------|-----------|------------------|

| 51025504      |                               | EP1A  | 2001      |                  |