Ce document a été numérisé par le <u>CRDP de Montpellier</u> pour la Base Nationale des Sujets d'Examens de l'enseignement professionnel

Ce fichier numérique ne peut être reproduit, représenté, adapté ou traduit sans autorisation.

**CODE: 1306-AER A T 21**

Ce dossier technique comporte 13 pages, numérotées de 1/13 à 13/13.

Assurez-vous que cet exemplaire est complet.

S'il est incomplet, demandez un autre exemplaire au chef de salle.

# **DOSSIER TECHNIQUE**

## **SOMMAIRE**

| INTRODUCTION                                        | 3  |

|-----------------------------------------------------|----|

| Présentation du système RADIO-ALTIMETRE sur l'avion | 3  |

| Equipement de bord du radio-altimètre               | 4  |

| Synoptique du système radio-altimètre               | 4  |

| CONVERSION TENSION / HAUTEUR DE VOL                 | 5  |

| GENERATION ELECTRIQUE                               | 6  |

| SYNOPTIQUE GENERATION ELECTRIQUE                    | 8  |

| CARTE RADIO ALTIMETER CONVERTER                     | 9  |

| MONTAGES FONDAMENTAUX AOP                           | 10 |

| BASCULES                                            |    |

| CONVERTISSEUR AD 7542                               | 11 |

| MICROCONTROLEUR 8748                                |    |

| CARACTERISTIQUE DE L'ATMOSPHERE                     | 12 |

| PRESENTATION DU THSA ET DE SON ATTACHE              | 13 |

| PLAN EN COUPE DE 1'ATTACHE                          | 13 |

#### **INTRODUCTION**

#### PRESENTATION DU SYSTEME

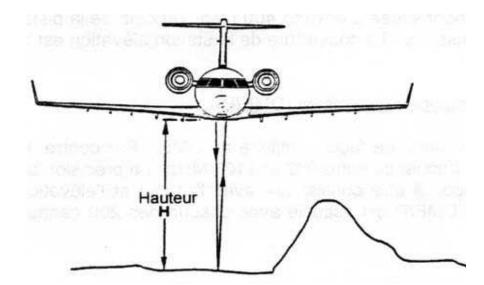

Le R.A. (radio-altimètre) mesure la hauteur de l'aéronef par rapport au sol.

La connaissance de cette hauteur est indispensable lors de l'atterrissage ou en approche I.L.S. (atterrissage aux instruments) en vol automatique.

Le EGPWS (système anticollision avec le sol) utilise également les informations d'altitude fournies par le RA. Le RA fournit une mesure bien plus précise que l'altimètre (mesure de pression) mais ne fonctionne que jusqu'à quelques milliers de pieds (2500 pieds sur la plupart des appareils). Lorsque l'avion touche le sol le RA donne 0 pied.

Le RA comprend 2 antennes, une d'émission (Transmitter Antenna) l'autre de réception (Receiver Antenna). Le principe de mesure est le calcul du temps mis par l'onde pour effectuer le trajet AVION-SOL-AVION.

La bande de fréquence d'émission radioélectrique allouée aux R.A. se situe entre 4200 MHz et 4400 MHz.

#### Présentation du système RADIO-ALTIMETRE sur l'avion

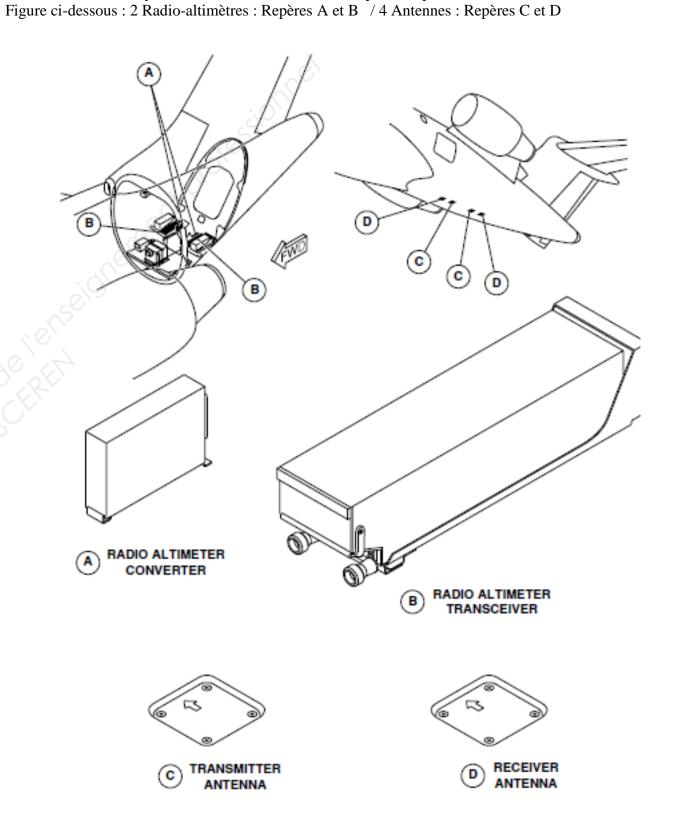

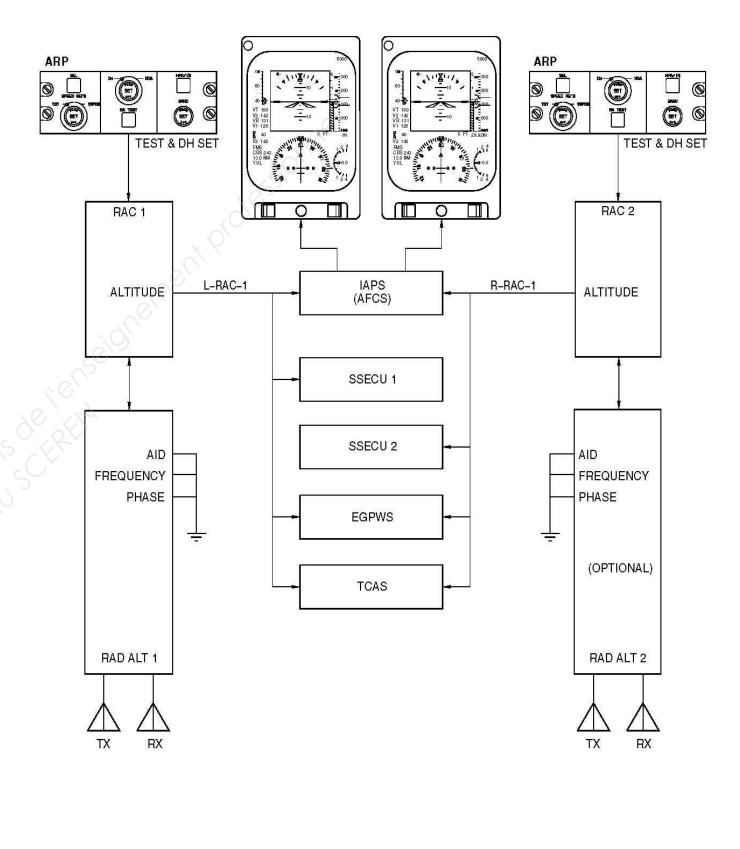

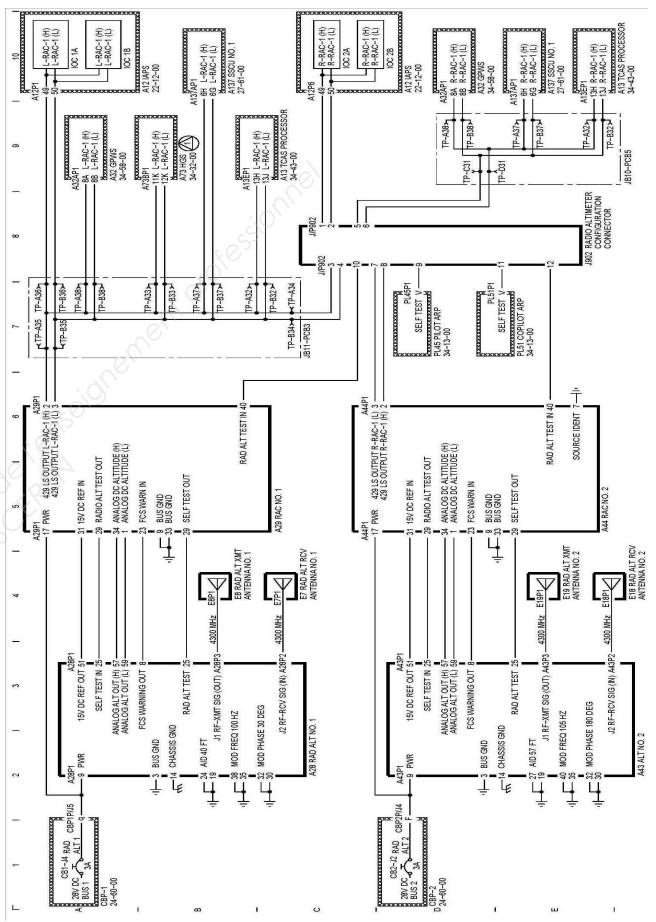

Le système radio-altimètre comprend les quatre éléments principaux A, B, C et D. L'avion utilise deux systèmes de mesure radio-altimétriques indépendants :

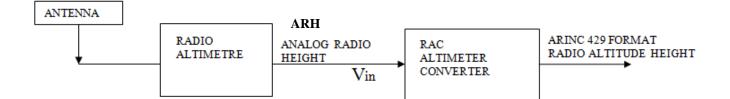

## Synoptique du système radio-altimètre

## Equipement de bord du radio-altimètre

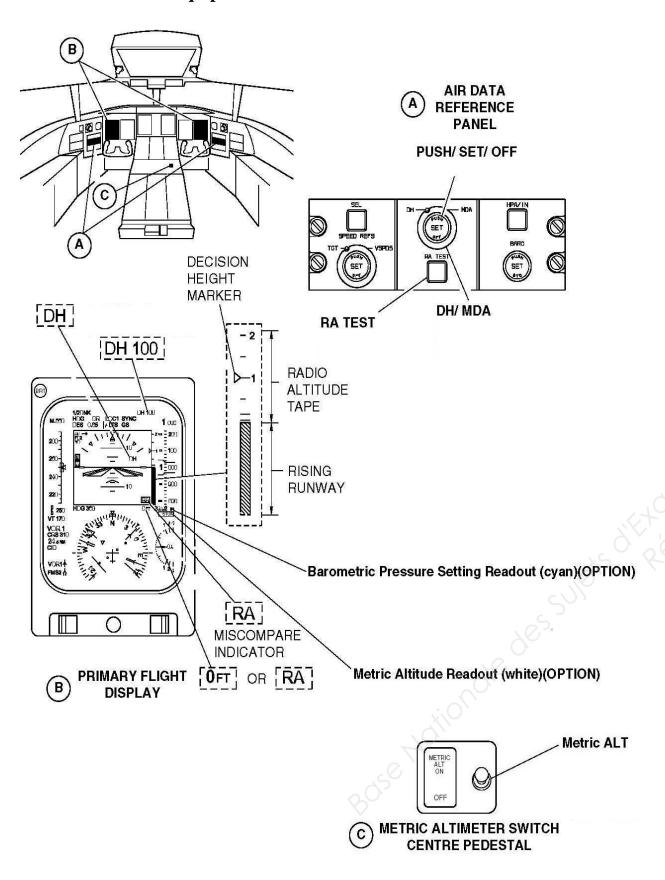

Le radio-altimètre mesure le temps mis par une onde électromagnétique pour faire l'aller-retour entre l'avion et le sol. Cette information « temps » est ensuite convertie en une tension Vin ( ANALOG RADIO HEIGHT) continue analogique.

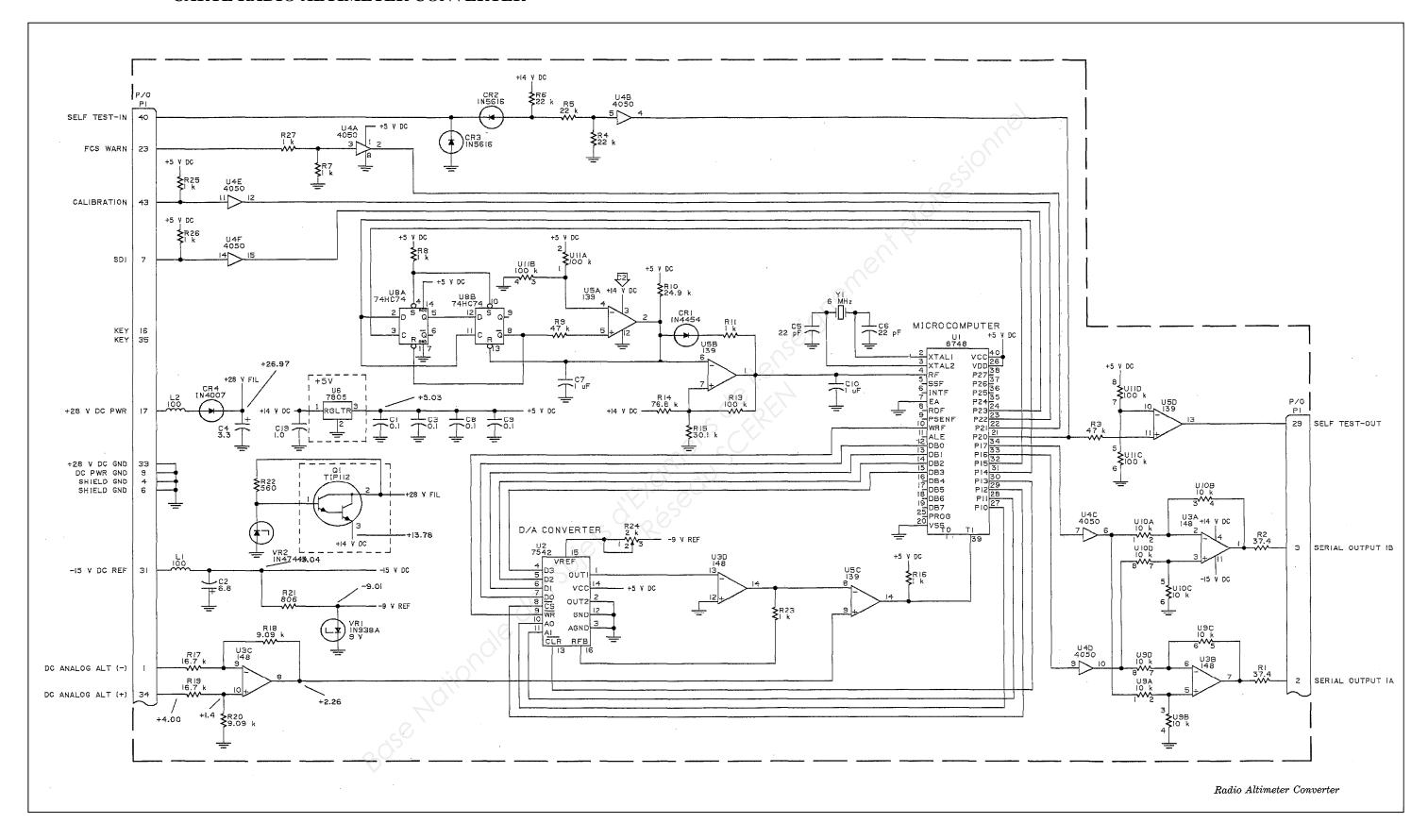

L'élément RAC (RADIO ALTIMETER CONVERTER) convertit la tension analogique Vin présente en entrée en une valeur numérique codée sur 12 bits grâce à un convertisseur analogique / numérique interne.

Cette valeur numérique est ensuite transmise aux différents systèmes avion en relation avec le système radioaltimétrique via le bus ARINC 429.

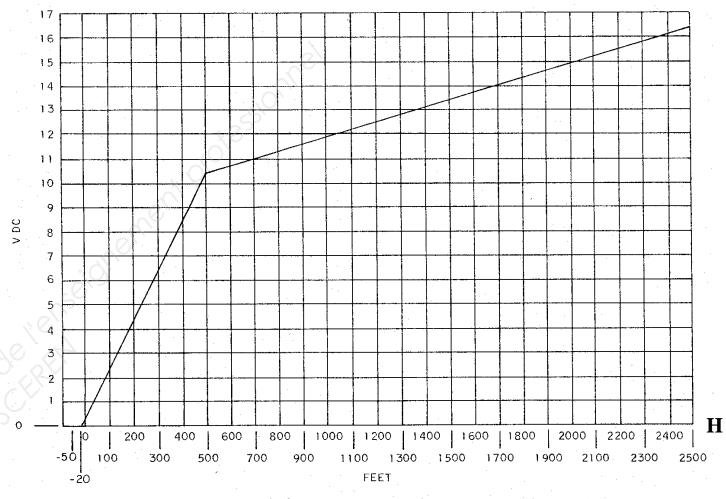

#### CONVERSION TENSION / HAUTEUR DE VOL

## **ARH**

NOTE: ARH = constante + (Résolution x Hauteur)

ANALOG PLOTTED USING THE FOLLOWING FORMULAS:

0 T0 500 FT:  $V = 0.4 \pm (0.02 \times H)$

500 T0 2500 FT: V = 10.4 + 0.003 X (H-500)

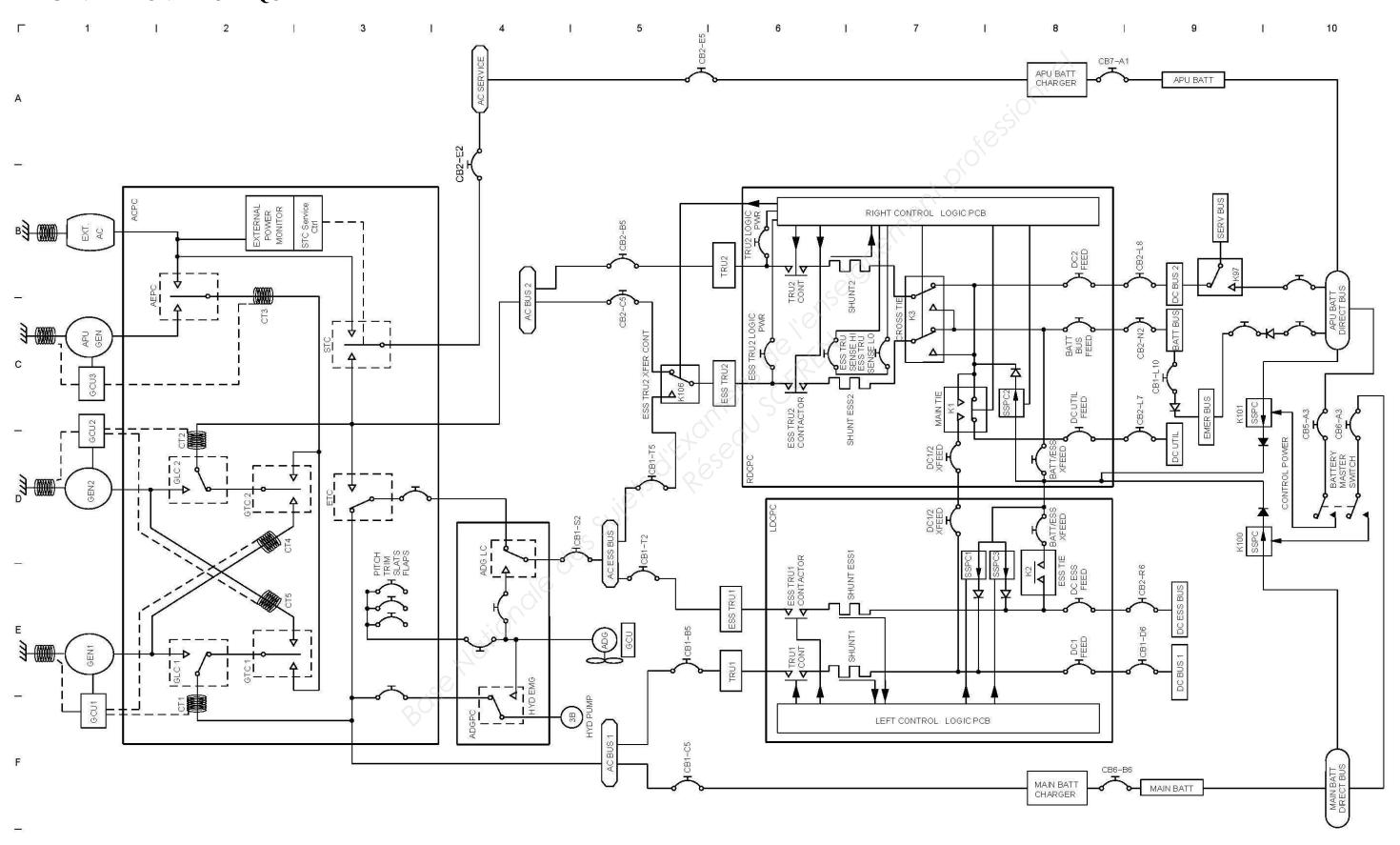

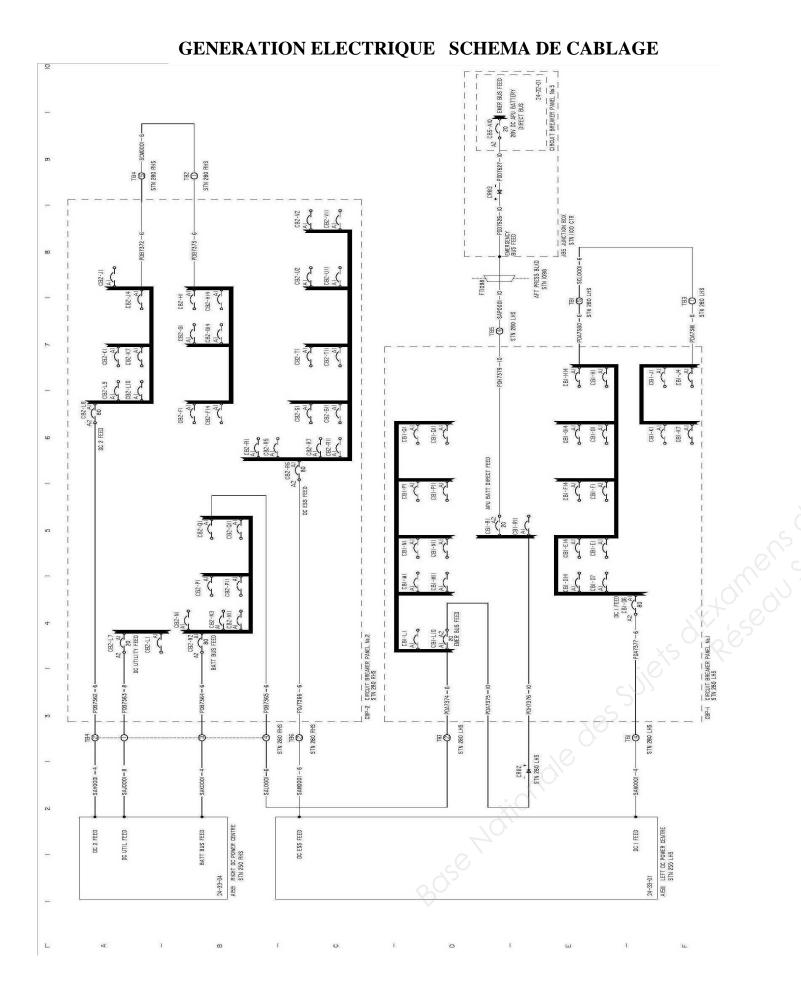

## **GENERATION ELECTRIQUE**

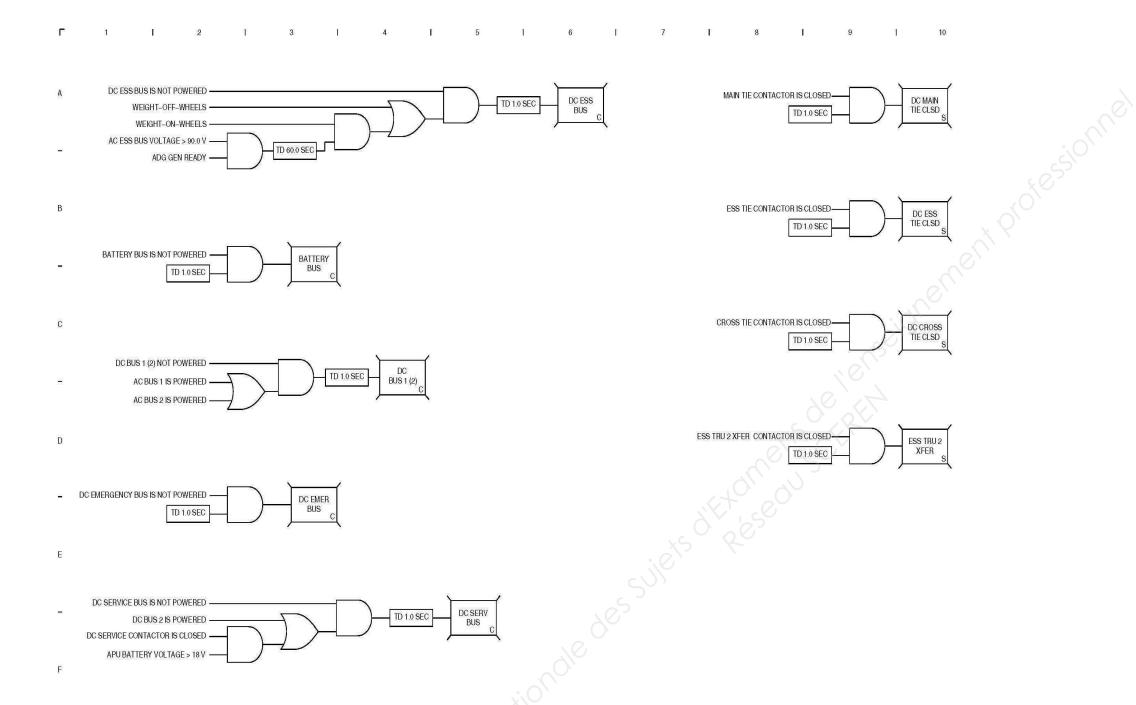

## SYNOPTIQUE GENERATION ELECTRIQUE

## CARTE RADIO ALTIMETER CONVERTER

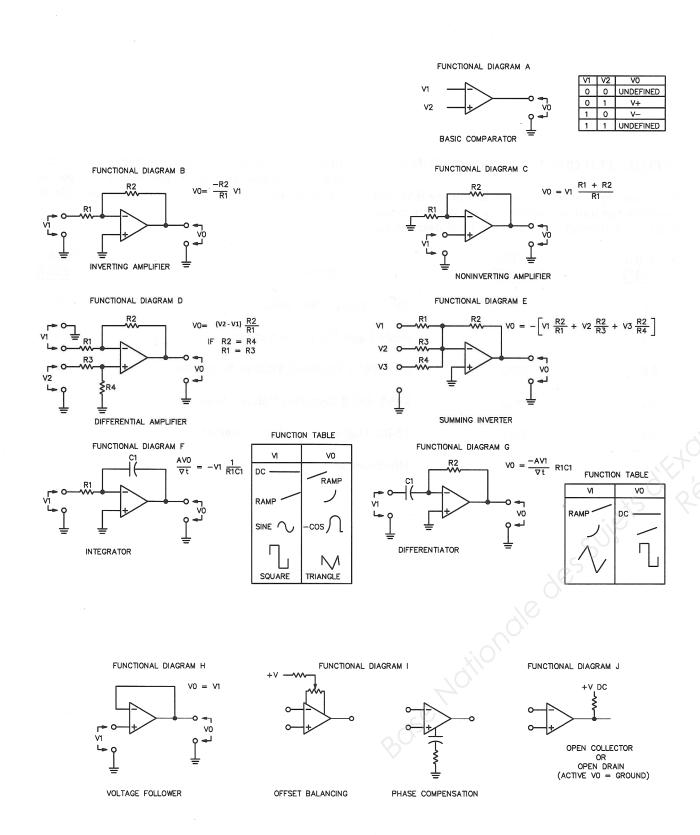

#### MONTAGES FONDAMENTAUX AOP

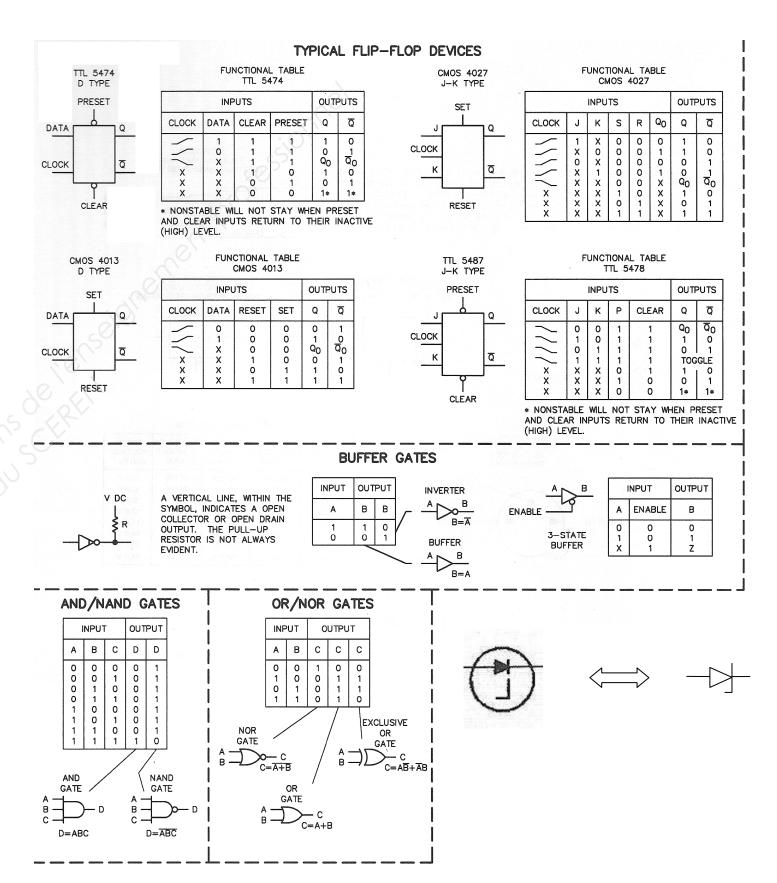

#### **BASCULES**

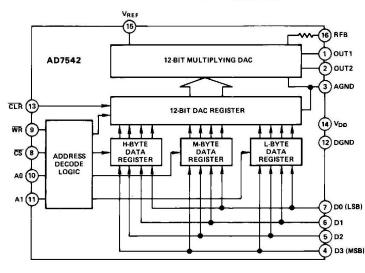

#### **CONVERTISSEUR AD 7542**

#### **FEATURES**

Resolution: 12 Bits

Nonlinearity:  $\pm 1/2$ LSB T<sub>min</sub> to T<sub>max</sub>

Low Gain Drift: 2ppm/°C typ, 5ppm/°C max

**Microprocessor Compatible Full 4-Quadrant Multiplication Fast Interface Timing**

Low Power Dissipation: 40mW max

**Low Cost**

Small Size: 16-pin DIP and 20-Terminal Surface

**Mount Package**

Latch Free (Protection Schottky Not Required)

#### **GENERAL DESCRIPTION**

The AD7542 is a precision 12-bit CMOS multiplying DAC designed for direct interface to 4- or 8-bit microprocessors.

The functional diagram shows the AD7542 to consist of three 4-bit data registers, a 12-bit DAC register, address decoding logic and a 12-bit CMOS multiplying DAC. Data is loaded into the data registers in three 4-bit bytes, and subsequently transferred to the 12-bit DAC register. All data loading or data transfer operations are identical to the WRITE cycle of a static RAM. A clear input allows the DAC register to be easily reset to all zeros when powering up the device.

Table IV. AD7542 Truth Table

| <del></del>    |                | AD7542 Operation |          |     |                                                                                                           |                                |

|----------------|----------------|------------------|----------|-----|-----------------------------------------------------------------------------------------------------------|--------------------------------|

| A <sub>1</sub> | A <sub>0</sub> | cs               | WR       | CLR | AD/342 Operation                                                                                          |                                |

| x              | x              | х                | x        | 0   | Resets DAC 12-Bit Register<br>to Code 0000 0000 0000                                                      |                                |

| х              | х              | 1                | x        | 1   | No Operation Device Not Selected                                                                          |                                |

| 0              | 0              | 0                | £        | 1   | Load LOW Byte <sup>5</sup><br>Data Register On<br>Edge As Shown                                           | Load                           |

| 0              | 1              | 0                | Æ        | 1   | Load MIDDLE Byte <sup>5</sup><br>Data Register On<br>Edge As Shown                                        | Applicable<br>Data<br>Register |

| 1              | 0              | 0                | <u>.</u> | 1   | Load HIGH Byte <sup>5</sup> Data Register On Edge As Shown With At D                                      |                                |

| 1              | 1              | 0                | Т        | 1   | Load 12-Bit DAC Register With<br>Data In LOW Byte, MIDDLE Byte<br>& HIGH Byte Data Registers <sup>6</sup> |                                |

NOTES:

<sup>1</sup> 1 indicates logic HIGH <sup>2</sup> 0 indicates logic LOW

MSB → XXXX XXXX XXXX ← LSB high byte middle

<sup>3</sup>X indicates don't care byte byte byte

<sup>4</sup> Indicates LOW to HIGH transition <sup>6</sup> These control signals are level triggered

#### **FUNCTIONAL BLOCK DIAGRAM**

The AD7542 is manufactured using an advanced thin-film on monolithic CMOS fabrication process. Multiplying capability, low power dissipation, +5V operation, small size (16-pin DIP and 20 terminal surface mount packages) and easy  $\mu P$  interface make the AD7542 ideal for many instrumentation, industrial control and avionics applications.

| PIN | MNEMONIC         | FUNCTION                                                                   |  |

|-----|------------------|----------------------------------------------------------------------------|--|

| 1   | OUT1             | DAC current output bus. Normally<br>terminated at op amp<br>virtual ground |  |

| 2   | OUT2             | DAC current output bus. Normally terminated at ground                      |  |

| 3   | AGND             | Analog Ground                                                              |  |

| 4   | D3               | Data Input (MSB)                                                           |  |

| 5   | D2               | Data Input                                                                 |  |

| 6   | D1               | Data Input                                                                 |  |

| 7   | D0               | Data Input (LSB)                                                           |  |

| 8   | CS               | Chip Select Input                                                          |  |

| 9   | WR               | WRITE Input                                                                |  |

| 10  | A0               | Address Bus Input                                                          |  |

| 11  | A1               | Address Bus Input                                                          |  |

| 12  | DGND             | Digital Ground                                                             |  |

| 13  | CLR              | Clear Input                                                                |  |

| 14  | $V_{DD}$         | +5V Supply Input                                                           |  |

| 15  | V <sub>REF</sub> | Reference Input                                                            |  |

| 16  | RFB              | DAC Feedback Resistor                                                      |  |

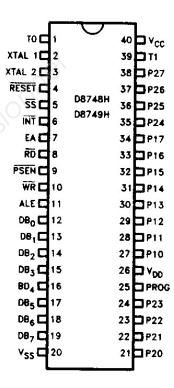

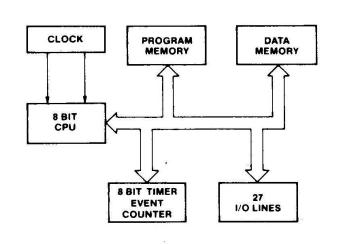

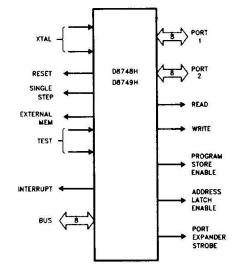

#### **MICROCONTROLEUR 8748**

| Device | Internal N   | lemory     |

|--------|--------------|------------|

| D8748H | 1K x 8 EPROM | 64 x 8 RAM |

**Block Diagram**

**Logic Symbol**

Table 1. Pin Description (40-Pin DIP)

| Symbol Pin No. Function           |       |                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-----------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| V <sub>SS</sub>                   | 20    | Circuit GND potential.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| V <sub>DD</sub> 26                |       | + 5V during normal operation.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                                   |       |                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| V <sub>CC</sub>                   | 40    | Programming power supply (+21V).                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| PROG                              | 25    | Main power supply; +5V during operation and programming.                                                                                                                                                                                                                                                                                                                                                         |  |  |

| ,ou                               | 2.0   | Output strobe for 8243 I/O expander.                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| P10-P17                           | 27-34 | Program pulse (+ 18V) input pin during programming.                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Port 1                            | 27-34 | 8-bit quasi-bidirectional port.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| P20-P23                           | 21-24 | 8-bit quasi-bidirectional port. P20-P23 contain the four high order program counter bits during an external program memory fetch and serve as a 4-bit I/O expander bus for 8243.                                                                                                                                                                                                                                 |  |  |

| P24-P27<br>Port 2                 | 35–38 |                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| DB0-DB7<br>BUS                    | 12-19 | True bidirectional port which can be written or read synchronously using th RD, WR strobes. The port can also be statically latched. Contains the 8 low order program counter bits during an external program memory fetch, and receives the addressed instruction under the control of PSEN. Also contain the address and data during an external RAM data store instruction, under control of ALE, RD, and WR. |  |  |

| T0 1 Input pin ter<br>T0 can be c |       | Input pin testable using the conditional transfer instructions JT0 and JNT0. T0 can be designated as a clock output using ENT0 CKL instruction.                                                                                                                                                                                                                                                                  |  |  |

|                                   |       | Used during programming.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| T1                                | 39    | Input pin testable using the JT1, and JNT1 instructions. Can be designate the timer/counter input using the STRT CNT instruction.                                                                                                                                                                                                                                                                                |  |  |

| INT                               | 6     | Interrupt input. Initiates an interrupt if interrupt is enabled. Interrupt is disabled after a reset. Also testable with conditional jump instruction. (Acti low) interrupt must remain low for at least 3 machine cycles for proper operation.                                                                                                                                                                  |  |  |

| RD                                | 8     | Output strobe activated during a BUS read. Can be used to enable data onto the bus from an external device. Used as a read strobe to external data memory. (Active low)                                                                                                                                                                                                                                          |  |  |

| Symbol  | Pin No. | Function                                                                                                                                                                          |  |  |  |

|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RESET 4 |         | Input which is used to initialize the processor. (Active low) (Non TTL VIH)                                                                                                       |  |  |  |

|         |         | Used during programming.                                                                                                                                                          |  |  |  |

| WR      | 10      | Output strobe during a bus write. (Active low) Used as write strobe to external data memory.                                                                                      |  |  |  |

| ALE     | 11      | Address latch enable. This signal occurs once during each cycle and is useful as a clock output.  The negative edge of ALE strobes address into external data and program memory. |  |  |  |

| PSEN    | 9       | Program store enable. This output occurs only during a fetch to external program memory. (Active low.)                                                                            |  |  |  |

| SS      | 5       | Single step input can be used in conjunction with ALE to "single step" the processor through each instruction.                                                                    |  |  |  |

| EA 7    |         | External access input which forces all program memory fetches to reference external memory. Useful for emulation and debug. (Active high.)                                        |  |  |  |

|         |         | Used during (18V) programming.                                                                                                                                                    |  |  |  |

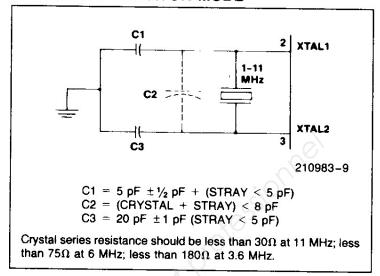

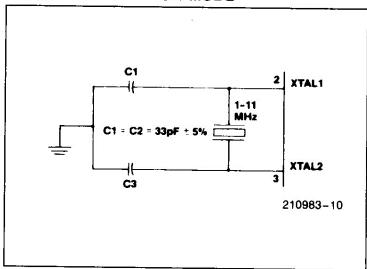

| XTAL1   | 2       | One side of crystal input for internal oscillator. Also input for external source. (Non TTL V <sub>IH</sub> .)                                                                    |  |  |  |

| XTAL2   | 3       | Other side of crystal input.                                                                                                                                                      |  |  |  |

# BACCALAURÉAT PROFESSIONNEL Aéronautique ÉPREUVE E2 – Epreuve de technologie Option Mécanicien, systèmes-avionique SOUS-ÉPREUVE A (U21) – Étude d'un système d'aéronef

## **CRYSTAL OSCILLATOR MODE**

#### **CERAMIC RESONATOR MODE**

## CARACTERISTIQUE DE L'ATMOSPHERE

DOSSIER TECHNIQUE

| Altitude<br>[m] | Température<br>[Kelvin] | Pression<br>[pascal] | Masse<br>volumique<br>[kg/m3] | Célérité<br>du son<br>[m/s] |

|-----------------|-------------------------|----------------------|-------------------------------|-----------------------------|

| 0               | 288.15                  | 101325               | 1.225                         | 340.29                      |

| 1000            | 281.65                  | 89874                | 1.1116                        | 336.43                      |

| 2000            | 275.15                  | 79495                | 1.0065                        | 332.52                      |

| 3000            | 268.65                  | 70108                | 0.9091                        | 328.57                      |

| 4000            | 262.15                  | 61640                | 0.8191                        | 324.57                      |

| 5000            | 255.65                  | 54019                | 0.7361                        | 320.52                      |

| 6000            | 249.15                  | 47181                | 0.6597                        | 316.42                      |

| 7000            | 242.65                  | 41060                | 0.5895                        | 312.27                      |

| 8000            | 236.15                  | 35599                | 0.5252                        | 308.06                      |

| 9000            | 229.65                  | 30742                | 0.4663                        | 303.79                      |

| 10000           | 223.15                  | 26436                | 0.4127                        | 299.46                      |

Durée : 4 h

Coef.: 2

Session 2013

PAGE 12/13

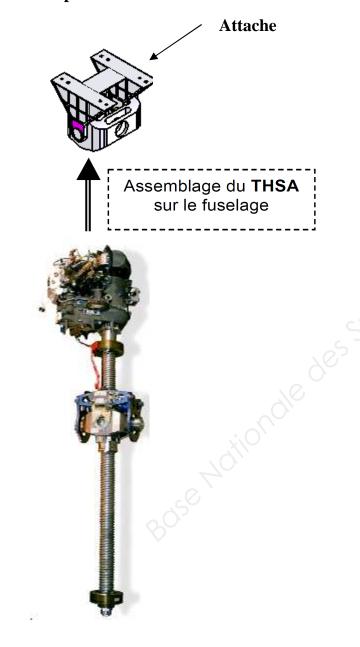

#### PRESENTATION DU THSA ET DE SON ATTACHE

Le plan horizontal arrière assure l'équilibre en tangage de l'appareil. Il se situe à l'extrémité arrière du fuselage. Il est en liaison pivot avec le fuselage arrière.

Le plan horizontal arrière réglable est appelé **THS** (Trimmable Horizontal Stabilizer).

## Son actionneur est appelé THSA (Trimmable Horizontal Stabilizer Actuator)

Le **THSA** a pour fonction d'assurer le positionnement angulaire du plan horizontal arrière en fonction des ordres venant soit du pilote (levier de commande), soit du calculateur de l'appareil (vol automatique). Il doit en outre maintenir le plan horizontal arrière en position en cas de défaillance.

#### Le THSA est reliée à la structure avion par une attache.

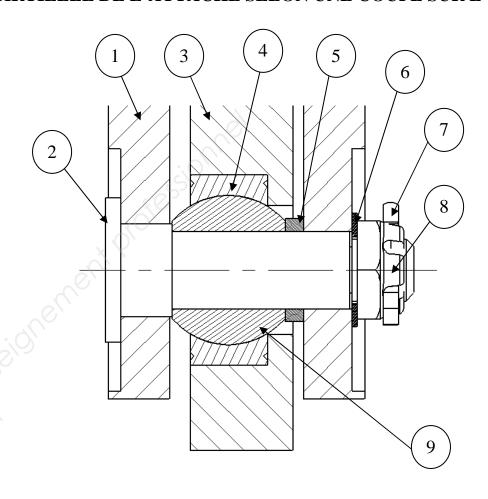

#### VUE PARTIELLE DE L'ATTACHE SELON UNE COUPE SUR L'AXE MEDIAN.

#### Nomenclature:

| Rep | Nbre | Désignation | Matière | Obs             |

|-----|------|-------------|---------|-----------------|

| 1   | 1    | Bâti        |         | Lié au fuselage |

| 2   | 1    | Axe         |         |                 |

| 3   | 1    | Berceau     |         |                 |

| 4   | 1    | Bague       |         |                 |

| 5   | 1    | Entretoise  |         |                 |

| 6   | 1    | Rondelle    |         |                 |

| 7   | 1    | Goupille    |         |                 |

| 8   | 1    | Ecrou       |         |                 |

| 9   | 1    | Rotule      |         |                 |